### Embedded Coder<sup>®</sup> Release Notes

# MATLAB&SIMULINK®

R

#### **How to Contact MathWorks**

Latest news:

Phone:

www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

$\searrow$

508-647-7000

#### The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

Embedded Coder<sup>®</sup> Release Notes

© COPYRIGHT 2011-2021 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ products\ are\ protected\ by\ one\ or\ more\ U.S.\ patents.\ Please\ see\ www.mathworks.com/patents\ for\ more\ information.$

#### **Check Bug Reports for Issues and Fixes**

Software is inherently complex and is not free of errors. The output of a code generator might contain bugs, some of which are not detected by a compiler. MathWorks reports critical known bugs brought to its attention on its Bug Report system at www.mathworks.com/support/bugreports/. In the search bar, type the phrase "Incorrect Code Generation" to obtain a report of known bugs that produce code that might compile and execute, but still produce wrong answers. To save a search, click Save Search.

The bug reports are an integral part of the documentation for each release. Examine periodically all bug reports for a release, as such reports may identify inconsistencies between the actual behavior of a release you are using and the behavior described in this documentation.

In addition to reviewing bug reports, you should implement a verification and validation strategy to identify potential bugs in your design, code, and tools.

## Contents

#### R2021b

| Code Generation from MATLAB Code                                                                                                                                                                                                     | 1-2                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

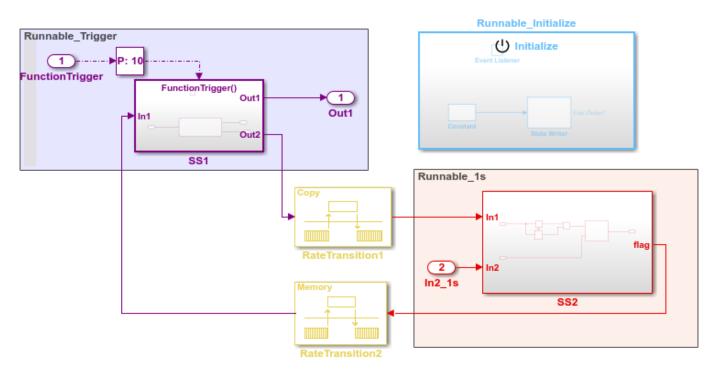

| Communication I/O information display during SIL or PIL execution<br>Visualization of task scheduling<br>Reduction of violations for MISRA C++:2008 and AUTOSAR C++14 rules in                                                       | 1-2<br>1-2           |

| generated code                                                                                                                                                                                                                       | 1-2                  |

| Model Architecture and Design                                                                                                                                                                                                        | 1-3                  |

| Built-in storage class for multi-instance data<br>Symbolic dimension inputs for Bitwise Operator, Saturation, and Data Type<br>Propagation blocks                                                                                    | 1-3<br>1-3           |

| Code Interface Configuration and Integration                                                                                                                                                                                         | 1-5                  |

| Storage class with pointer data access in Embedded Coder Dictionary<br>Unstructured Embedded Coder Dictionary storage class application to                                                                                           | 1-4                  |

| model reference root I/O<br>Embedded Coder Dictionary storage class application to signals and<br>parameters with symbolic dimensions                                                                                                | 1-4<br>1-4           |

| Changes to model hierarchy requirements       Calibration file customization         TLC code storage classes in default mapping       Calibration                                                                                   | 1-4<br>1-5<br>1-5    |

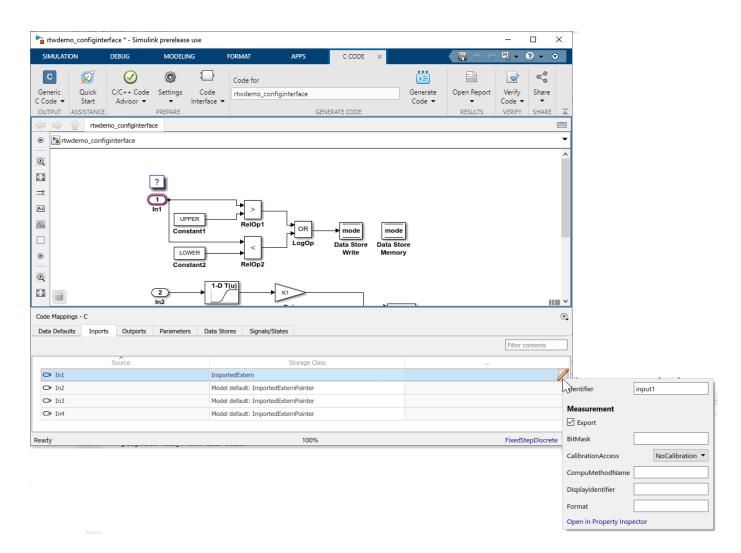

| Configure additional properties from the Code Mappings editor<br>View In Bus Element and Out Bus Element blocks in a hierarchy in the Code                                                                                           | 1-5                  |

| Mappings editor<br>Configuring C/C++ function prototypes for subsystems not recommended                                                                                                                                              | 1-6                  |

| Reusable storage class in Code Mappings editor<br>Generated C++ model class name can be the model name                                                                                                                               | 1-6<br>1-7<br>1-7    |

| Code Generation                                                                                                                                                                                                                      | 1-8                  |

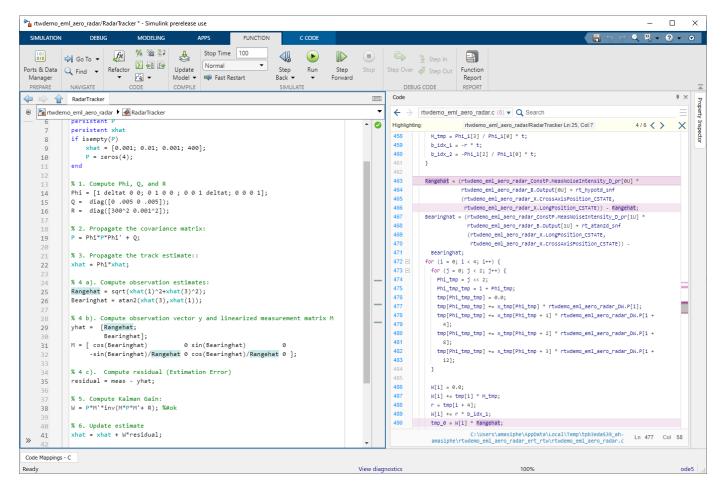

| Accessibility of step entry-point functions generated for models designed for<br>multitasking and concurrency streamlined<br>Code view for MATLAB Function block<br>Enhanced code to reduce MISRA C:2012 Rule 10.3 and Directive 4.1 | 1-8<br>1-9           |

| Changes to generated C++ header files                                                                                                                                                                                                | 1-10<br>1-10<br>1-10 |

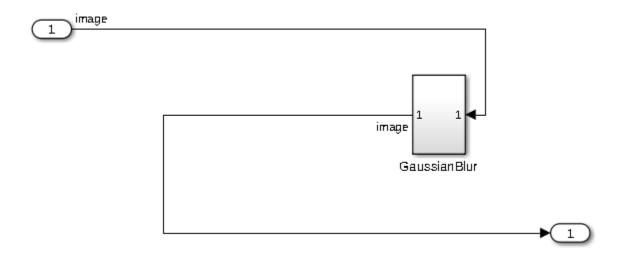

| Minimized variable visibility for C++ code       Image data by using OpenCV class cv::Mat                                                                                                                                            | 1-11<br>1-12<br>1-13 |

|                                                                                                                                                                                                                                      | 1-14                 |

| Deployment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-15                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| <ul> <li>New TLC variable OverrideSampleERTMain for disabling generation of example main program</li> <li>Texas Instruments C2000: Code generation support for Configurable Logic Block (CLB) and CLB X-Bar in Embedded Coder Support Package for Texas Instruments C2000 Processors</li> <li>Texas Instruments C2000: External Mode Simulation Using XCP on CAN Interface</li> <li>Support for STMicroelectronics STM32F4xx-based Boards</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                | 1-15<br>1-15<br>1-15<br>1-15                                                                 |

| Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-16                                                                                         |

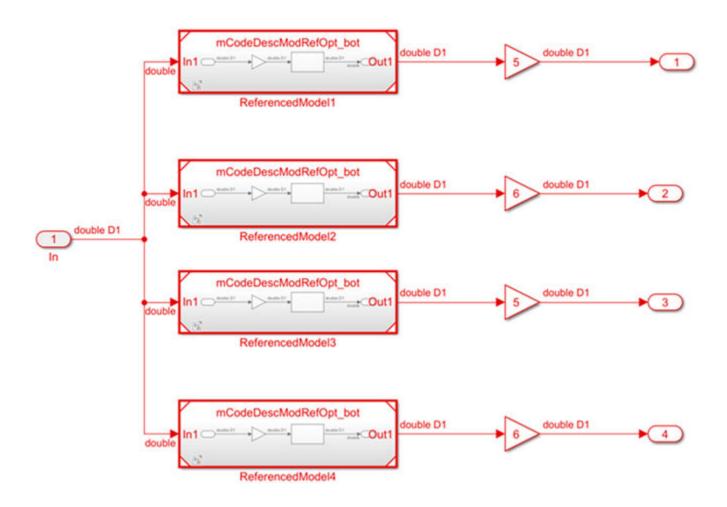

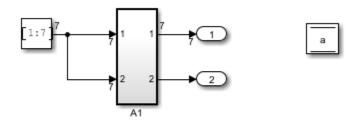

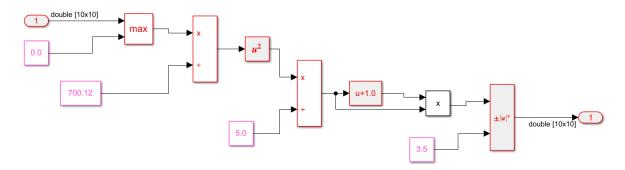

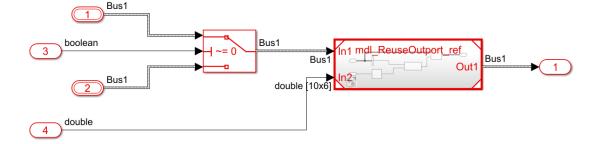

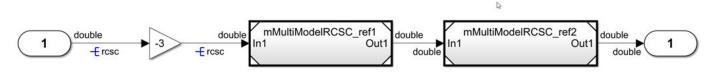

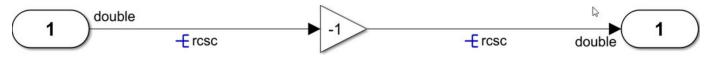

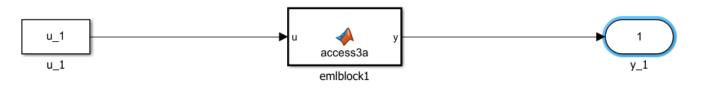

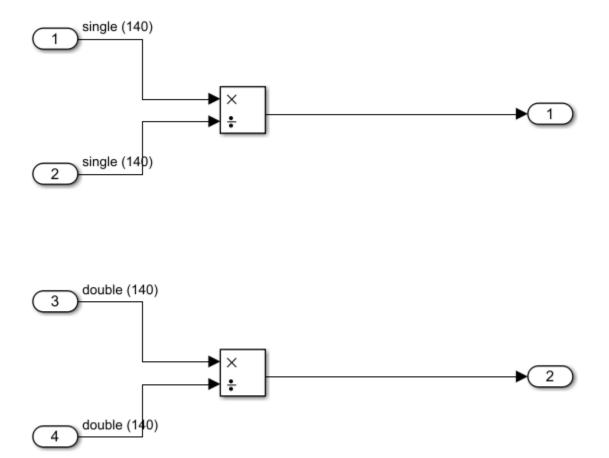

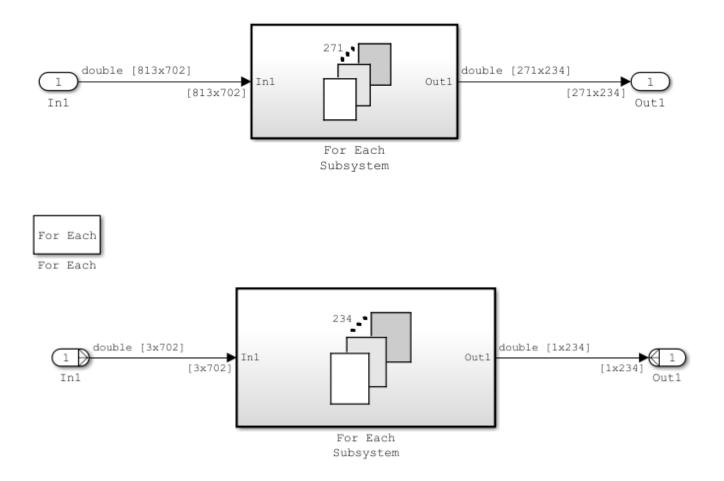

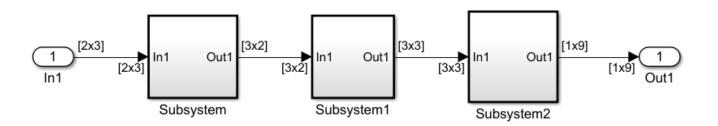

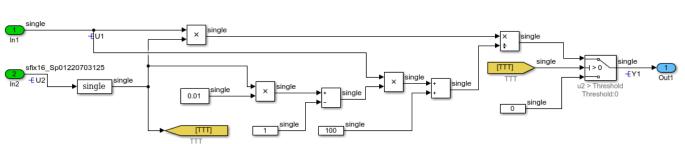

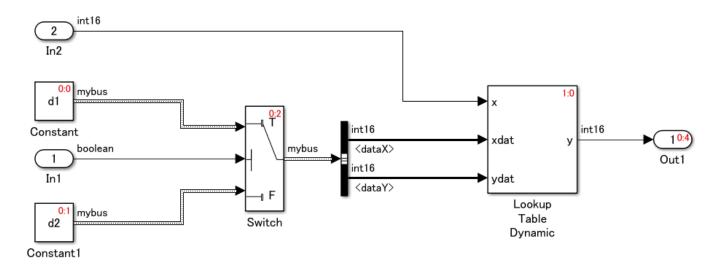

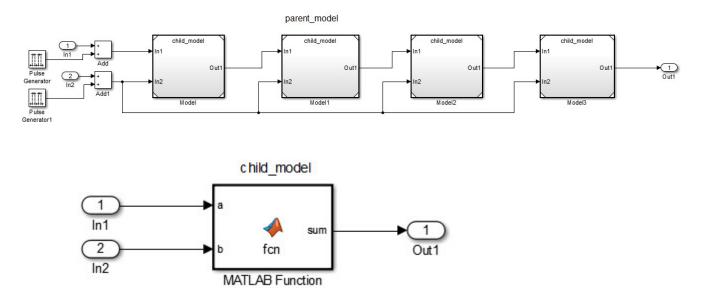

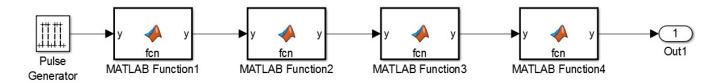

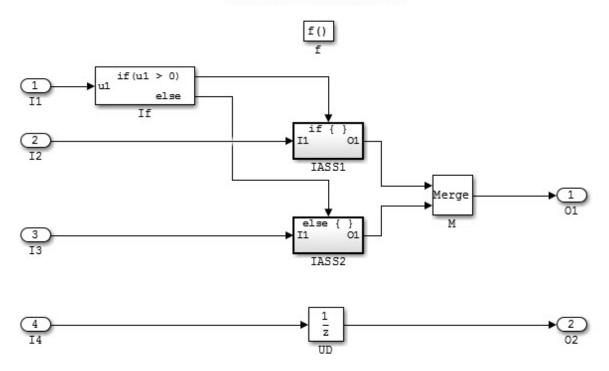

| Generation of SIMD code by using new configuration parameterImage Processing Toolbox functions enhanced with multithreading and<br>algorithm improvementsReduced data copies for models that have Bus Creator blocksSIMD optimization for more integer data typesRoot outport initialization code performance improvementsReadability improvement for root outport initialization codeOptimize code by unrolling parallel for-loopsImproved common subexpression eliminationOptimized SIMD code that performs fused multiply add operationsRedundant data copies elimination by reusing S-function block buffersOptimized code for models containing referenced modelsNonstatic data class member initialization of instance-specific parametersCode replacement for trigonometric functions that use lookup table<br>approximation | 1-16<br>1-17<br>1-19<br>1-20<br>1-21<br>1-22<br>1-22<br>1-23<br>1-24<br>1-26<br>1-27<br>1-28 |

| Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-29                                                                                         |

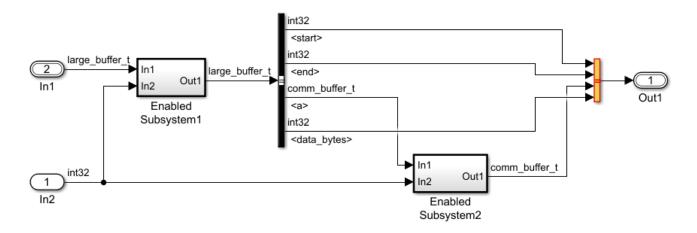

| Communication I/O information display during SIL or PIL simulation<br>Signal and state logging for SIL and PIL simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-29<br>1-29<br>1-29                                                                         |

| Check bug reports for issues and fixes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-30                                                                                         |

#### R2021a

| Code Generation from MATLAB Code                                                                                                                                                          | 2-2        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Multiple signature for software-in-the-loop (SIL) and processor-in-the-loop<br>(PIL) execution<br>Reduction of violations for MISRA C++:2008 and AUTOSAR C++14 rules in<br>generated code | 2-2<br>2-2 |

| Format generated code by using clang-format                                                                                                                                               | 2-3        |

| Model Architecture and Design                                                                                                                                                             | 2-4        |

| Step entry-point functions generated for rate-based and concurrent execution models declared in model.h                                                                                   | 2-4        |

| Code Interface Configuration and Integration                                                                                                                                                                                                                                    | 2-5                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| C++ class interface configuration by using a code mappings workflow<br>Instance specific parameter support for C++ class interfaces<br>Auto data initialization for new storage classes<br>Dimension preservation of multidimensional arrays for Simulink.Bus object            | 2-5<br>2-5<br>2-5               |

| Calibration file generation<br>Code configuration for data dictionary defaults<br>ASAP2 system target file being removed<br>Functionality being removed or changed                                                                                                              | 2-6<br>2-6<br>2-6<br>2-6<br>2-6 |

| Code Generation                                                                                                                                                                                                                                                                 | 2-8                             |

| Enhanced generated code to reduce MISRA C:2012 Rule 12.2 violations<br>Removal of typedef from C++ struct definitions<br>Braced variable initialization for C++ 11 library<br>Code generation and SIL or PIL simulations for protected models from<br>R2018b and later releases | 2-8<br>2-8<br>2-8<br>2-9        |

| Performance                                                                                                                                                                                                                                                                     | 2-10                            |

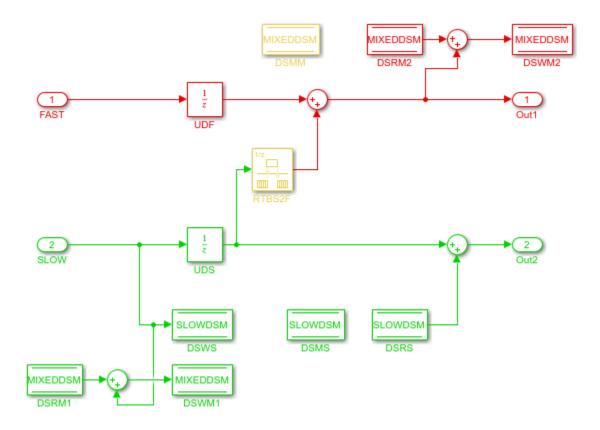

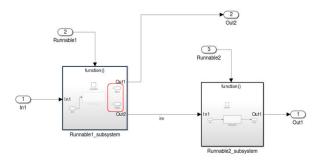

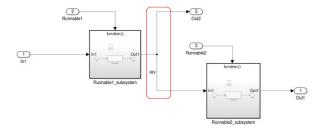

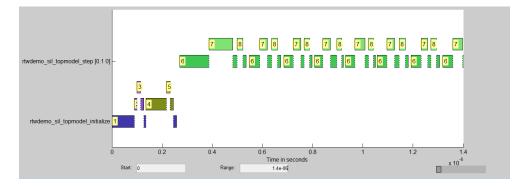

| Code execution profiling information in Code view<br>Visualization of task scheduling<br>Removal of instrumentation overhead from execution-time profiling by using                                                                                                             |                                 |

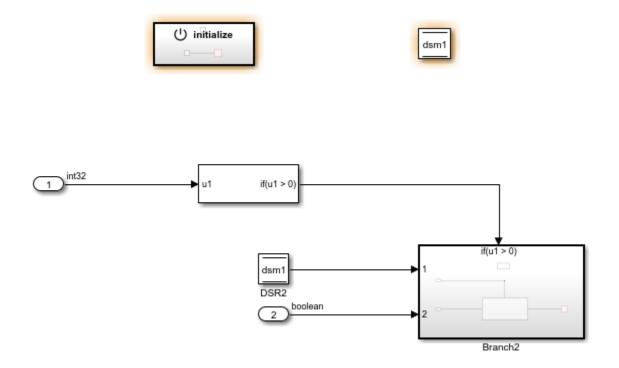

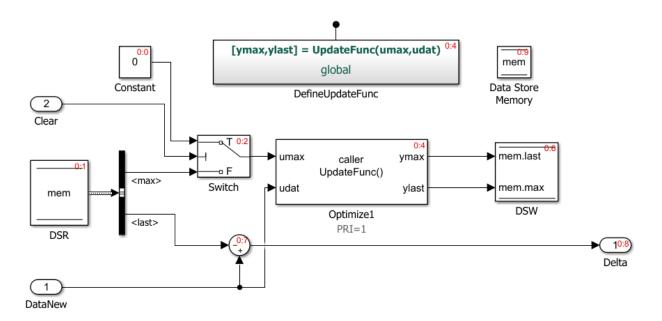

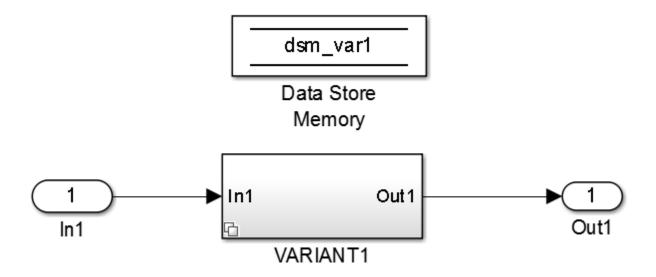

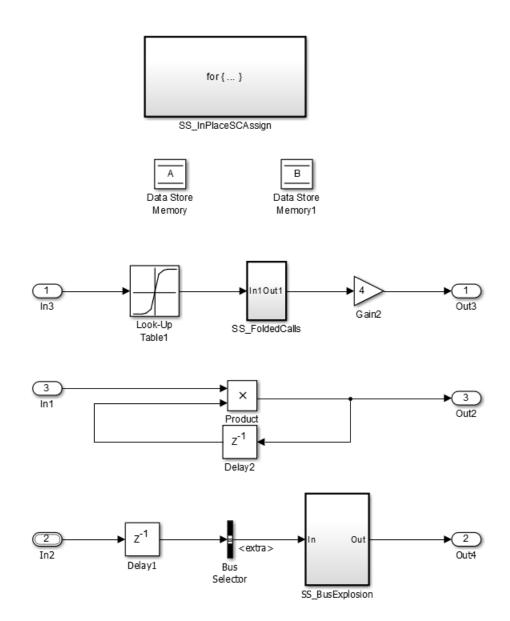

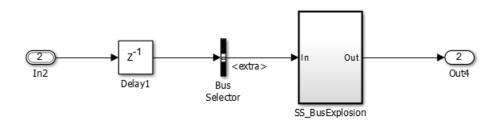

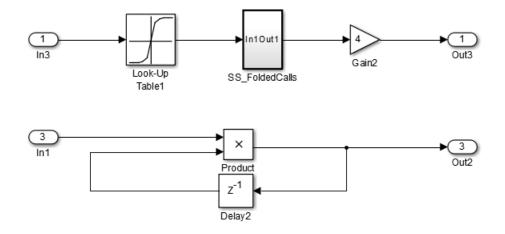

| target package<br>Enhanced code for models containing mask blocks or Data Store Memory<br>blocks<br>GCC ARM Cortex-A code replacement library contains other ARM libraries                                                                                                      | 2-10<br>2-11                    |

| Multithreading capabilities for more Image Processing Toolbox functions                                                                                                                                                                                                         | 2-11                            |

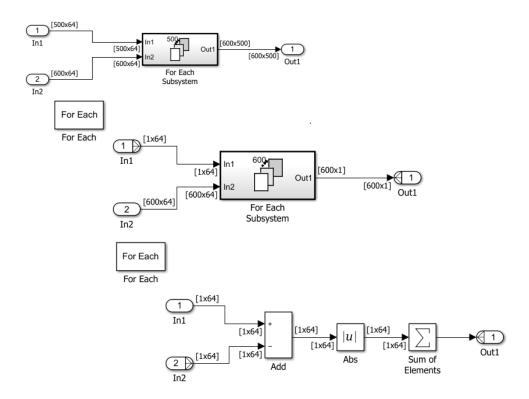

| Improved cache performance of generated code containing distributed loop                                                                                                                                                                                                        | 2-12<br>2-13                    |

| nests                                                                                                                                                                                                                                                                           | 2-13<br>2-15<br>2-16<br>2-17    |

| Verification                                                                                                                                                                                                                                                                    | 2-19                            |

| PIL target connectivity with debugger                                                                                                                                                                                                                                           | 2-19                            |

| model                                                                                                                                                                                                                                                                           | 2-19<br>2-19                    |

| Check bug reports for issues and fixes                                                                                                                                                                                                                                          | 2-21                            |

#### R2020b

| Model Architecture and Design |  | 3-2 |

|-------------------------------|--|-----|

|-------------------------------|--|-----|

| Determine programmatically if model or data dictionary contains Embedded<br>Coder Dictionary                                                                                                                                                                                                                                                                                                                                                           | i<br><b>3-</b> 2                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

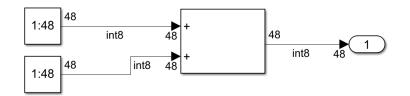

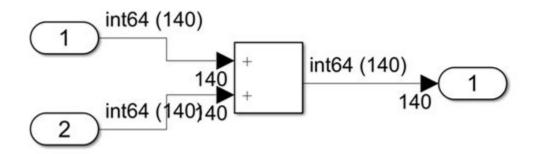

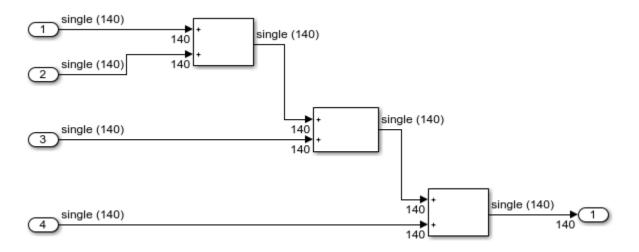

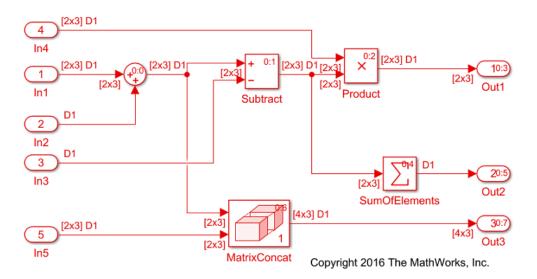

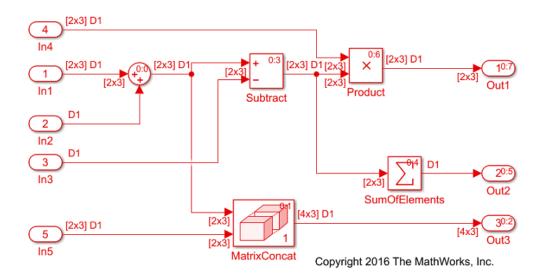

| Symbolic dimension inputs for Add, Subtract, Sum of Elements, and Sum                                                                                                                                                                                                                                                                                                                                                                                  |                                                      |

| blocks<br>Improved readability for preprocessor conditionals in generated code<br>Memory section configurations for atomic subsystems                                                                                                                                                                                                                                                                                                                  | 3-2<br>3-2<br>3-3                                    |

| Code Interface Configuration and Integration                                                                                                                                                                                                                                                                                                                                                                                                           | 3-4                                                  |

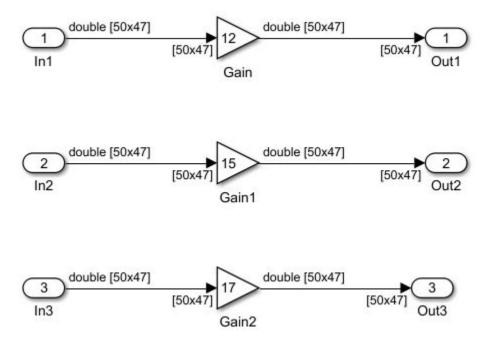

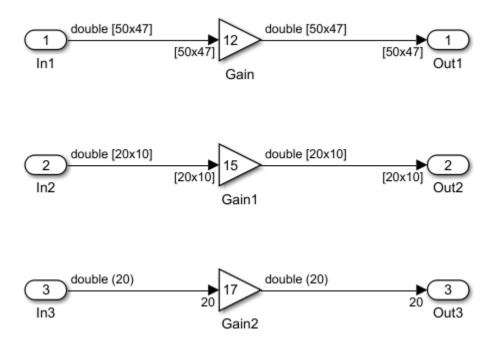

| Streamlined model data configuration for code generation<br>Dimension preservation of multidimensional arrays for individual model                                                                                                                                                                                                                                                                                                                     | 3-4                                                  |

| elements                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-5<br>3-6<br>3-6                                    |

| Code Generation                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-12                                                 |

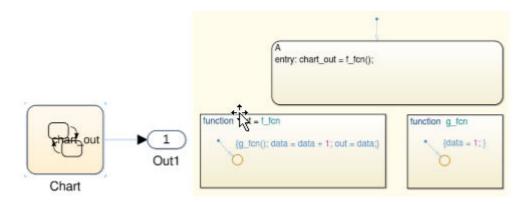

| Static code metrics for C99 and C++ libraries<br>Code generation using multiple code replacement libraries<br>Static reusable subsystem functions for C++ class interface<br>Name mangling of functions inside MATLAB Function block code<br>Generated code enhanced to reduce MISRA C:2012 Rule 13.5 violations                                                                                                                                       | 3-12<br>3-12<br>3-12<br>3-13                         |

| Generate static code metrics report programmatically<br>Code generation and SIL or PIL simulations for protected models from                                                                                                                                                                                                                                                                                                                           | 3-13<br>3-13                                         |

| R2018b and later releases Cross-release code integration for non-finite numbers in shared utility code                                                                                                                                                                                                                                                                                                                                                 | 3-14                                                 |

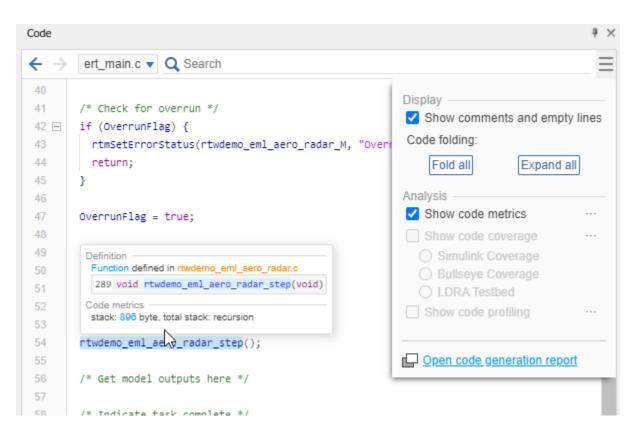

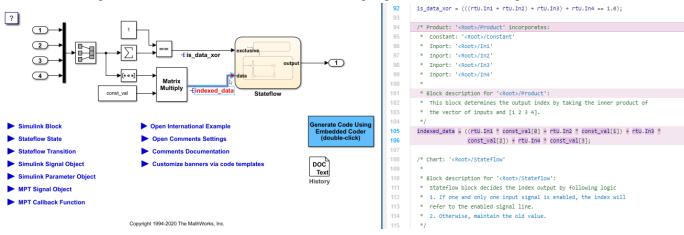

| Enhanced traceability between variables and modeling elements in Code                                                                                                                                                                                                                                                                                                                                                                                  | 3-14                                                 |

| view                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-14                                                 |

| Standardization of header guards in header files                                                                                                                                                                                                                                                                                                                                                                                                       | 3-15<br>3-15                                         |

| Deployment                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-16                                                 |

| <ul> <li>Texas Instruments C2000: Support of UDP and Hardware Interrupt Blocks<br/>for F2838x (ARM Cortex-M4) Processor in Embedded Coder Support<br/>Package for Texas Instruments C2000 Processors</li> <li>Texas Instruments C2000: Support Code Generation for SDFM Module in<br/>F2807x, F2837x, F28004x and F2838x Processors for Embedded Coder<br/>Support Package for Texas Instruments C2000 Processors</li> </ul>                           | 3-16<br>3-16                                         |

| Performance                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-17                                                 |

| SIMD code generated using Intel AVX-512 code replacement library<br>Improved cache performance of generated code that has loop interchange                                                                                                                                                                                                                                                                                                             | 3-17                                                 |

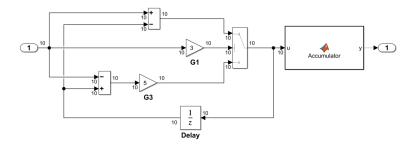

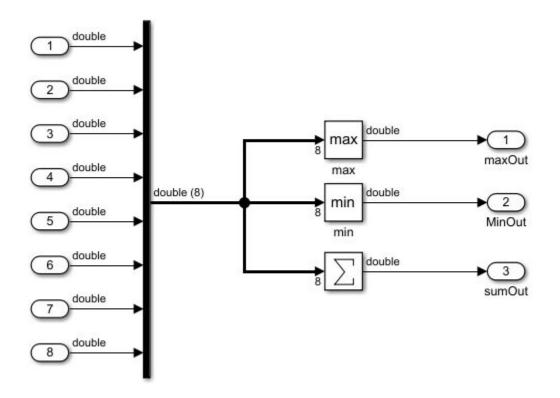

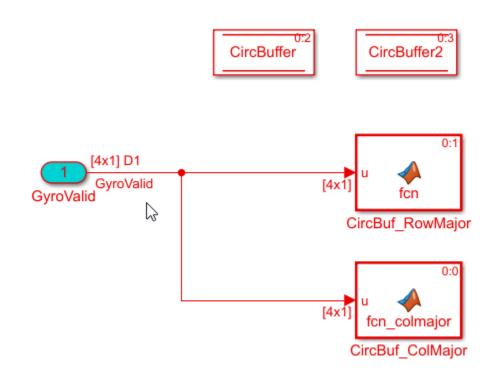

| SIMD vectorization of loops in Simulink models          Generated code optimization through SIMD for integer data type          Enhanced Image Processing Toolbox functions in generated code          Distribution of execution times for generated code internal functions          Hardware timer for code execution profiling during PIL simulations          Caching of array elements to scalar variables reduces computations in generated code | 3-18<br>3-20<br>3-21<br>3-22<br>3-24<br>3-24<br>3-24 |

| Verification                                       | 3-26         |

|----------------------------------------------------|--------------|

| Target connectivity for PIL simulations            | 3-26         |

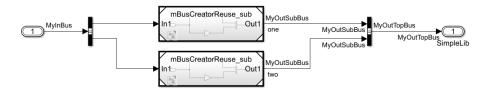

| SIL and PIL testing of reusable library subsystems | 3-26<br>3-26 |

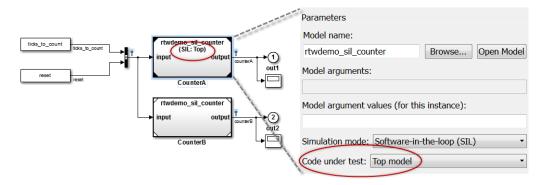

| Removal of top-model SIL and PIL limitations       | 3-27         |

| SIL/PIL Manager settings                           | 3-27<br>3-28 |

| Functionality being removed or changed             | 3-28         |

| Check bug reports for issues and fixes             | 3-29         |

#### R2020a

| Code Generation from MATLAB Code                                                                                                                                                                                                                                                                                                                                             | 4-2                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Model Architecture and Design                                                                                                                                                                                                                                                                                                                                                | 4-3                          |

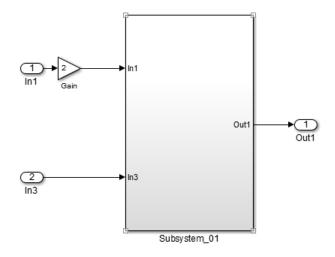

| <ul> <li>Function arguments to match graphical block interface for nonreusable subsystems</li> <li>External I/O visibility for C++ class interface</li> <li>C++ message-based communication provides length argument for service functions</li> <li>Zero initialization code model configuration parameters disabled for C++</li> </ul>                                      | 4-3<br>4-3<br>4-3            |

| class interface                                                                                                                                                                                                                                                                                                                                                              | 4-4                          |

| Code Interface Configuration and Integration                                                                                                                                                                                                                                                                                                                                 | 4-5                          |

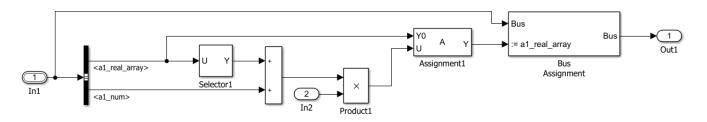

| Alias property of Simulink.CoderInfo renamed Identifier<br>Model type definitions within class namespace<br>Dimension preservation of multidimensional arrays for Data Store Memory                                                                                                                                                                                          | 4-5<br>4-5                   |

| blocks, states, and signals<br>Storage class change for model workspace parameter converted to<br>Simulink.Parameter                                                                                                                                                                                                                                                         | 4-5<br>4-6                   |

| Functionality being removed or changed                                                                                                                                                                                                                                                                                                                                       | 4-0<br>4-7                   |

| Code Generation                                                                                                                                                                                                                                                                                                                                                              | 4-8                          |

| std::array support in C++ code generation<br>Allow Arguments for non-reusable subsystems with C++<br>\$R token in Memory Sections of Embedded Coder Dictionary<br>Reduction in identifier collisions in model reference hierarchy<br>Static code metrics in Code view without code generation report<br>SIL or PIL simulations with protected model AUTOSAR code from R2018b | 4-8<br>4-8<br>4-9<br>4-9     |

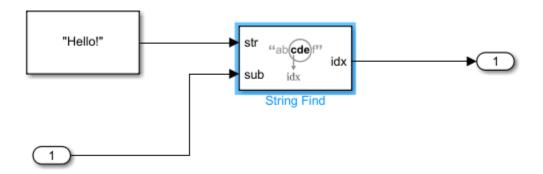

| or later<br>Storage classes on signal lines<br>Removal of preprocessor guards in C++ code<br>Removal of configuration parameter limitations for Simulink string code<br>generation                                                                                                                                                                                           | 4-10<br>4-10<br>4-10<br>4-10 |

| Deployment                                                                                                                                                                                                                                                                                                                                                                   | 4-12                         |

| FFT code replacement library (CRL) support for ARM Cortex-A and Cortex-<br>M processors                                                                                                                                                                                                                                                                                                                               | 4-12                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Performance                                                                                                                                                                                                                                                                                                                                                                                                           | 4-13                                 |

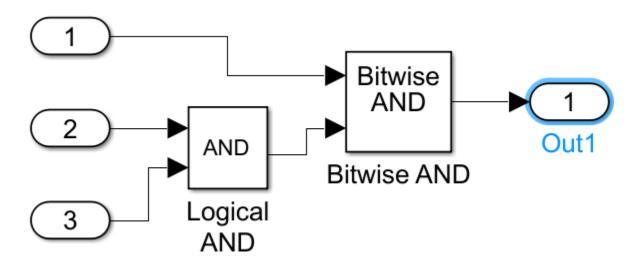

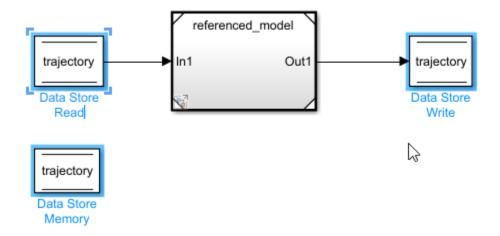

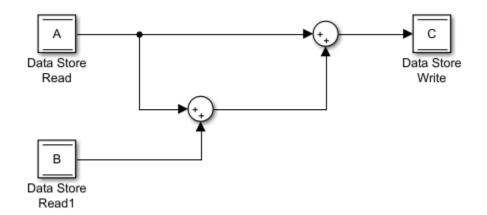

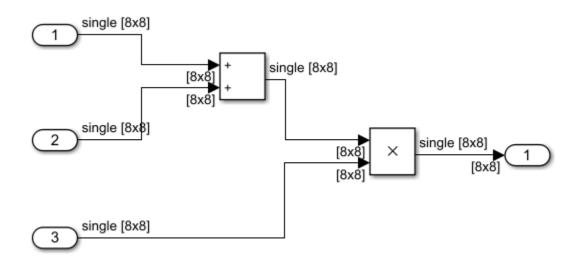

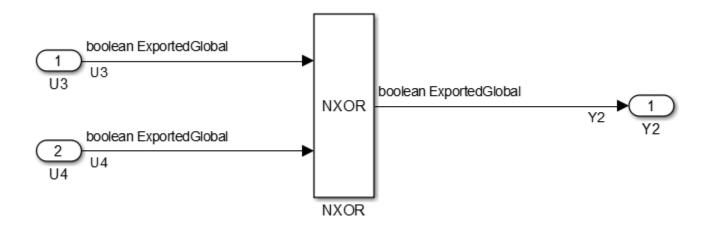

| Data Store Memory block reuse to reduce data copies in subsystems<br>Buffer reuse optimization for multidimensional arrays<br>Logical operators conversion to bitwise operators in generated code<br>Enhanced Image Processing Toolbox functions in generated code<br>Capture main code execution profiling metrics on target hardware<br>Efficient code for model-reference builds in presence of function prototype | 4-13<br>4-15<br>4-16<br>4-17<br>4-18 |

| control                                                                                                                                                                                                                                                                                                                                                                                                               | 4-18<br>4-19                         |

| Check bug reports for issues and fixes                                                                                                                                                                                                                                                                                                                                                                                | 4-20                                 |

#### R2019b

| Code Generation from MATLAB Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-2                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Customize C/C++ code file names generated from MATLAB code<br>Custom type definitions from external header files<br>Disable generation of initialize function<br>Function profiling for SIL and PIL execution                                                                                                                                                                                                                                                                                                                                                 | 5-2<br>5-2<br>5-2<br>5-2               |

| Model Architecture and Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-3                                    |

| Symbolic dimension support for Stateflow Data<br>Generate C++ Code for Software Compositions with Message-Based<br>Communication<br>Cut, copy, and paste code definitions in Embedded Coder Dictionary<br>Configure Embedded Coder Dictionary programmatically                                                                                                                                                                                                                                                                                                | 5-3<br>5-3<br>5-3<br>5-3               |

| Data, Function, and File Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-5                                    |

| <ul> <li>Generated code calibration and monitoring through XCP and third-party tools</li> <li>Argument specifications not required for Function Caller blocks that invoke scoped Simulink functions</li> <li>Implicit validation occurs when configuring C function prototypes</li> <li>Map storage classes defined in Embedded Coder Dictionary to nonreusable subsystems with separate data</li> <li>Code Mappings Editor Changes</li> <li>Function rtw.asap2SetAddress extracts DWARF debug symbols from binaries compiled using MinGW compiler</li> </ul> | 5-5<br>5-5<br>5-5<br>5-5<br>5-6<br>5-6 |

| Code Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-7                                    |

| Optimized C++ generated code for reusable functions<br>Embedded Coder contextual tabs on the Simulink Toolstrip<br>Simulink strings through standard C++ string library<br>C++ static_cast in generated code                                                                                                                                                                                                                                                                                                                                                  | 5-7<br>5-7<br>5-8<br>5-10              |

| Inline traceability for variable and type definitions                                                                                                                  | 5-10         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Deployment                                                                                                                                                             | 5-12         |

| Performance                                                                                                                                                            | 5-13         |

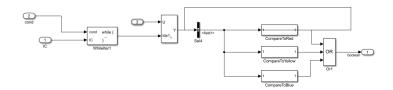

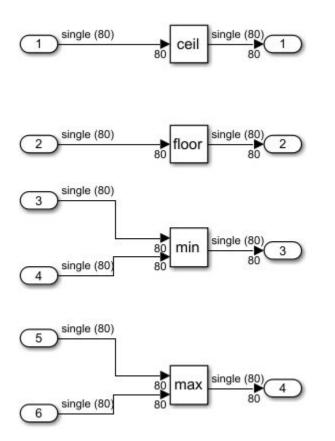

| Improved Data Store Memory block reuse to reduce data copies<br>SIMD vectorization for loops<br>Optimized code execution speed for Ceiling, Floor, Minimum and Maximum | 5-13<br>5-14 |

| SIMD intrinsic functions                                                                                                                                               | 5-14         |

| SIMD vectorization for loops without compile-time bounds                                                                                                               | 5-16<br>5-18 |

| Specification of upper constraint limit for symbolic dimensions                                                                                                        | 5-19         |

| Parameter expression saturation Changes to zero initialization code model configuration parameter default                                                              | 5-21         |

| settings                                                                                                                                                               | 5-21         |

| Enhanced code execution profiling report                                                                                                                               | 5-22         |

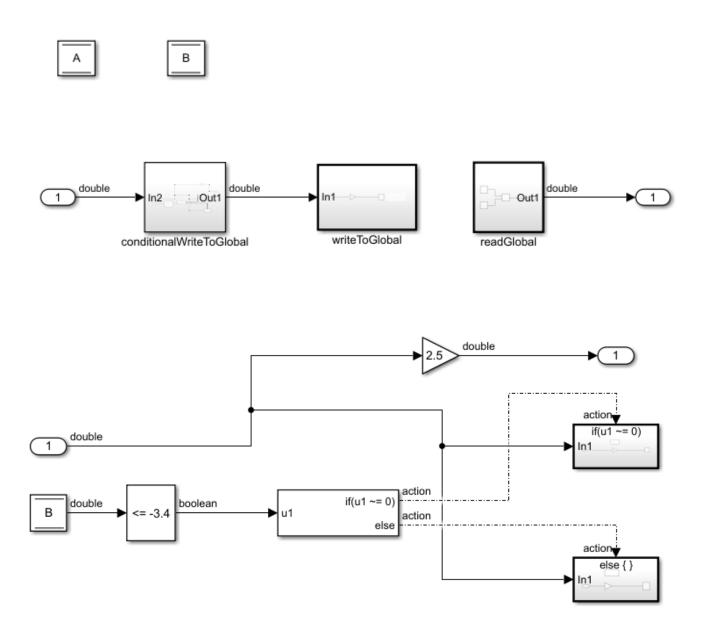

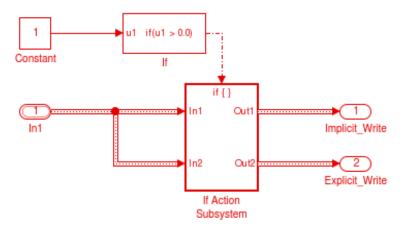

| Elimination of unused writes to global variables                                                                                                                       | 5-23         |

| Verification                                                                                                                                                           | 5-26         |

| SIL/PIL Manager                                                                                                                                                        | 5-26         |

| Code coverage information in Code view Data logging and signal viewer block support for export function models                                                         | 5-26         |

| SIL/PIL for AUTOSAR Classic Software Components containing referenced                                                                                                  | 5-26         |

| models                                                                                                                                                                 | 5-26<br>5-27 |

|                                                                                                                                                                        | J=2/         |

| Check bug reports for issues and fixes                                                                                                                                 | 5-28         |

#### R2019a

| Code Generation from MATLAB Code                                                                                                                                     | 6-2               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Custom Data Type Replacement: Specify custom data type names for<br>MATLAB data types                                                                                | 6-2               |

| Model Architecture and Design                                                                                                                                        | 6-3               |

| Library-based code generation for reusable subsystem function interfaces<br>AUTOSAR Blockset product replaces Embedded Coder Support Package for<br>AUTOSAR Standard | 6-3<br>6-3<br>6-3 |

| Data, Function, and File Definition                                                                                                                                  | 6-5               |

| Preserve array dimensions for root-level inports and outports in generated code                                                                                      | 6-5               |

| Custom storage class with different code generation settings for single-                                                                                                                                                                                     | c =          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| instance and multi-instance dataCode generation definitions in multiple packages from Embedded Coder                                                                                                                                                         | 6-5          |

| Dictionary                                                                                                                                                                                                                                                   | 6-6          |

| Storage classes with get and/or set data access functions in Embedded                                                                                                                                                                                        | 6-6          |

| Coder Dictionary Code definitions from local and shared Embedded Coder Dictionaries                                                                                                                                                                          | 0-0<br>6-6   |

| Code packaging support for model arguments                                                                                                                                                                                                                   | 6-7          |

| Model argument support for top models                                                                                                                                                                                                                        | 6-7          |

| C entry-point function prototype preview and customization in the Code<br>Mapping Editor                                                                                                                                                                     | 6-7          |

|                                                                                                                                                                                                                                                              |              |

| Code Generation                                                                                                                                                                                                                                              | 6-9          |

| Code metrics information in code viewCode view<br>Cross-release code import without opening previous release<br>Import of code from previous release for code generation-only workflow                                                                       | 6-9<br>6-9   |

| Movimum line width for generated and                                                                                                                                                                                                                         | 6-10<br>6-10 |

| Maximum line width for generated code       Symbolic dimension support for %roll directive                                                                                                                                                                   | 6-10<br>6-11 |

| Embedded Coder contextual tabs on the Simulink Toolstrip Tech Preview                                                                                                                                                                                        |              |

|                                                                                                                                                                                                                                                              | 6-12         |

| Deployment                                                                                                                                                                                                                                                   | 6-13         |

| <ul> <li>Embedded Coder Support Package for PX4 Autopilots: Generate, build and deploy Simulink models on Pixhawk flight controllers</li> <li>DSP System Toolbox Support Packages for ARM Cortex -A and ARM Cortex - M Processors will be removed</li> </ul> | 6-13<br>6-13 |

| Performance                                                                                                                                                                                                                                                  | 6-14         |

| Reusable custom storage classes across referenced models                                                                                                                                                                                                     | 6-14         |

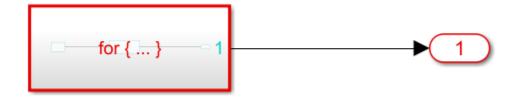

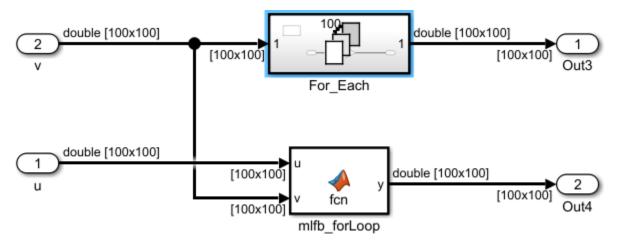

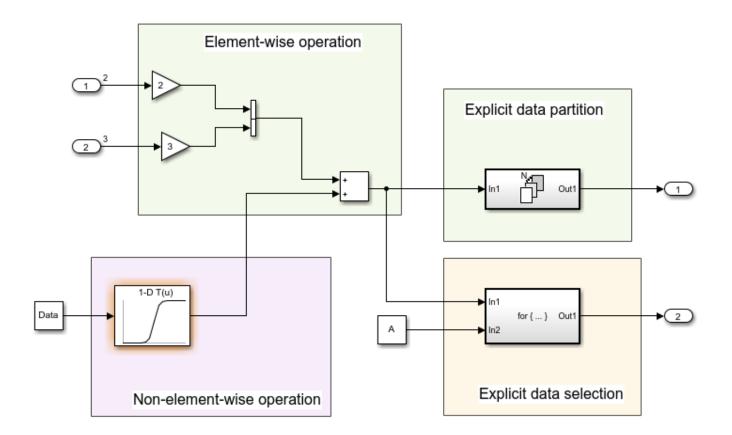

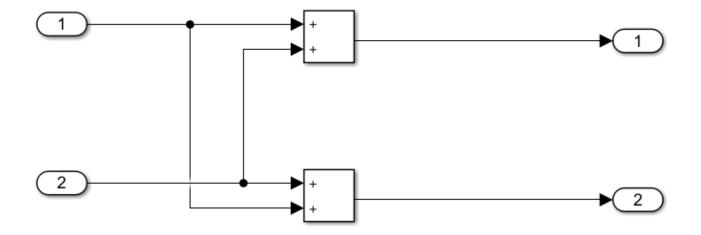

| Parallelization of execution of for-loopsSubsystem output with internal signals for buffer reduction                                                                                                                                                         | 6-15<br>6-16 |

| Optimized code execution speed for Single Instruction, Multiple Data                                                                                                                                                                                         | 0-10         |

| (SIMD) intrinsic division operation                                                                                                                                                                                                                          | 6-17         |

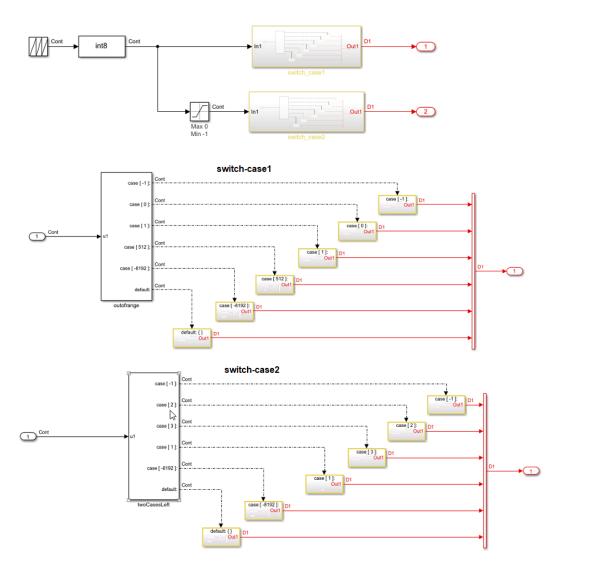

| Optimized code for Switch Case blocks                                                                                                                                                                                                                        | 6-19<br>6-22 |

| Improvement in execution speed through common subexpression                                                                                                                                                                                                  | •            |

| elimination                                                                                                                                                                                                                                                  | 6-22         |

| Data copy reduction in function calls                                                                                                                                                                                                                        | 6-24<br>6-25 |

|                                                                                                                                                                                                                                                              |              |

| Verification                                                                                                                                                                                                                                                 | 6-26         |

| Check bug reports for issues and fixes                                                                                                                                                                                                                       | 6-27         |

|                                                                                                                                                                                                                                                              |              |

#### R2018b

| Code Generation from MATLAB Code       7 | 7-2 |

|------------------------------------------|-----|

|------------------------------------------|-----|

| Column Limit in Generated Code: Generate more readable code by                                                                                                                                                |              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| controlling line wrapping Static Code Metrics On Demand: Run static code metrics analysis when                                                                                                                | 7-2          |

| needed after code generation                                                                                                                                                                                  | 7-2          |

| Single Instruction, Multiple Data (SIMD) Support: Generate Intel SSE/AVX intrinsic in MATLAB Coder                                                                                                            | 7-3          |

|                                                                                                                                                                                                               | /-3          |

| Model Architecture and Design                                                                                                                                                                                 | 7-4          |

| Multi-Instance Code Generation: Generate multi-instance code for top and referenced models that are based on rates, exported functions, or rates                                                              |              |

| and exported functions                                                                                                                                                                                        | 7-4          |

| Code Preview in Embedded Coder Dictionary: Verify pseudocode preview as<br>you select data, function, and memory section properties<br>Embedded Coder Dictionary Mapping Control: Define storage classes that | 7-4          |

| restrict mappings to parameters or signals                                                                                                                                                                    | 7-4          |

| Embedded Coder Dictionary Version Handling: Use and export code definitions saved in previous releases with models created in later                                                                           |              |

|                                                                                                                                                                                                               | 7-4          |

| AUTOSAR Run-Time Calibration: Map internal signals, states, and model<br>workspace parameters to AUTOSAR component memory and internal<br>parameters for calibration                                          | 7-5          |

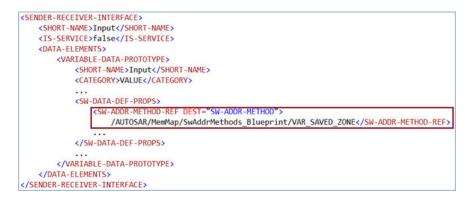

| AUTOSAR Memory Sections: Use SwAddrMethods to control memory                                                                                                                                                  | /-J          |

| placement of AUTOSAR runnable functions and internal data                                                                                                                                                     | 7-6          |

| AUTOSAR XML Import and Export: Round trip imported arxml file structure<br>and control packaging of new elements                                                                                              | 7-6          |

| AUTOSAR XML Import: Changes to ArTypedPerInstanceMemory and                                                                                                                                                   |              |

| StaticMemory import behavior                                                                                                                                                                                  | 7-7<br>7-7   |

| Obsolete AUTOSAR signal and state map functions removed<br>MISRA C:2012 and Secure Coding Standards: Improve compliance of                                                                                    | /-/          |

| generated code by using updated Model Advisor checks                                                                                                                                                          | 7-8          |

| Data, Function, and File Definition                                                                                                                                                                           | 7-9          |

| Individual Function Mappings in Code Mapping Editor: Override default                                                                                                                                         |              |

| function mappings with individual function mappings<br>Function Interface Control: Access Configure C Step Function Interface                                                                                 | 7-9          |

| dialog box from Code Mapping Editor in code perspective                                                                                                                                                       | 7-9          |

| Function Interface Control: Configure step functions for multi-instance,                                                                                                                                      |              |

| rate-grouped, single-tasking modelsShared Default Code Configurations for Data and Functions: Share default                                                                                                   | 7-10         |

| 5                                                                                                                                                                                                             | 7-10         |

| Storage Class on Root-Level I/O: Access global data and functions in multi-                                                                                                                                   | - 40         |

| instance models                                                                                                                                                                                               | 7-10         |

| Code Generation                                                                                                                                                                                               | 7-11         |

| Code View in Code Perspective: View generated code directly in Code                                                                                                                                           |              |

| Perspective                                                                                                                                                                                                   | 7-11         |

| operation                                                                                                                                                                                                     | 7-11         |

| AUTOSAR Code Generation: Automatically generate AUTOSAR platform                                                                                                                                              | 7 1 1        |

|                                                                                                                                                                                                               | 7-11<br>7-12 |

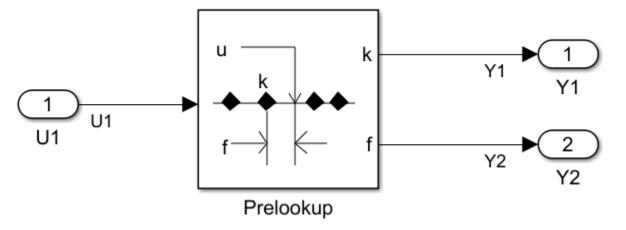

| Multi-Dimensional Arrays: Preserve array dimensions for parameters and                                                                                                                                        |              |

| lookup tables in generated code                                                                                                                                                                               | 7-12         |

| Hardware Implementation Parameters: ProdHWDeviceType and                                                                                                                                                                                                                                                              |                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| TargetHWDeviceType are case-insensitive          Enumerated Types: Optimizations in generated code                                                                                                                                                                                                                    | 7-14<br>7-14                 |

| Deployment                                                                                                                                                                                                                                                                                                            | 7-16                         |

| Texas Instruments C2000: Use DMA and CAN blocks for all supported C28x devices with the addition of DMA for F28x7x/F28004x and CAN for                                                                                                                                                                                |                              |

| F28004x<br>Code Generation Assumptions: Use standalone workflow to run checks .<br>Build Process: Library and header files for model reference hierarchy are                                                                                                                                                          | 7-16<br>7-16                 |

| not copied                                                                                                                                                                                                                                                                                                            | 7-16                         |

| makefiles<br>STM32F7 Tuning and Monitoring: Perform external mode simulation on<br>STM32F7 for parameter tuning and signal monitoring by using XCP over<br>TCP/IP or UART (Serial)                                                                                                                                    | 7-17<br>7-17                 |

| Performance                                                                                                                                                                                                                                                                                                           | 7-18                         |

| Execution-Time Profiling: Specify profiling granularity through model-wide<br>and block-specific controls                                                                                                                                                                                                             | 7-18<br>7-18                 |

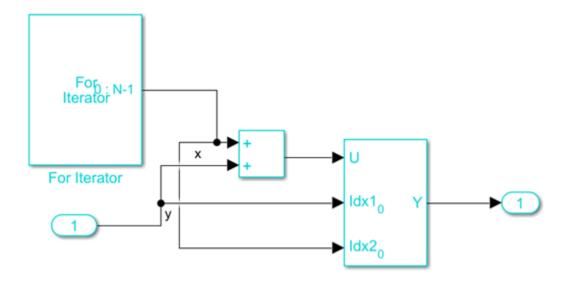

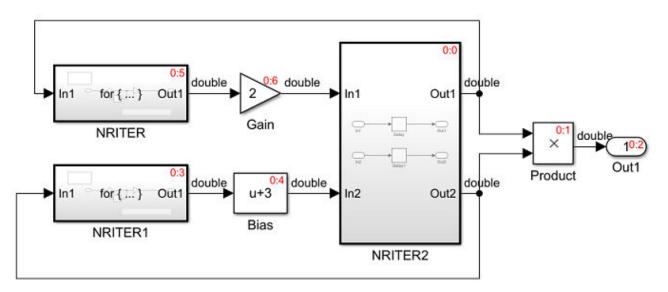

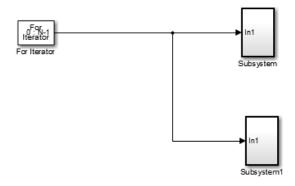

| Data Copy Reduction: Eliminate unnecessary data copies for Mux blocks<br>Enhanced Buffer Reuse: Buffer reuse across the boundary of an Iterator                                                                                                                                                                       | 7-20                         |

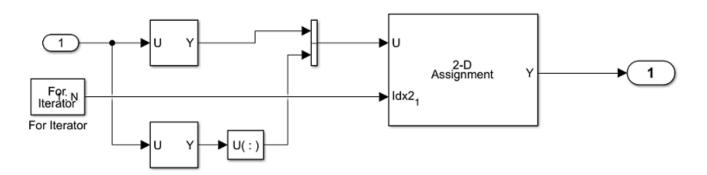

| subsystem                                                                                                                                                                                                                                                                                                             | 7-22<br>7-24                 |

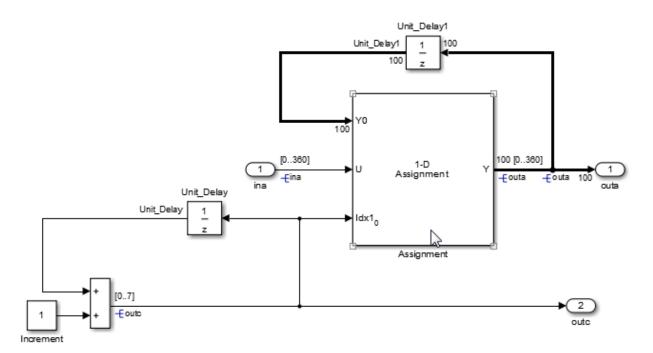

| Inplace Optimization for Assignment Blocks: Reduce data copies for         Assignment blocks         Execution Speed: Eliminate redundant subexpressions         Single Instruction, Multiple Data (SIMD) Intrinsics: Generate code with         optimized load and store operations for multidimensional signals and | 7-25<br>7-26                 |

| Square root operations       Square root operations         Code Generation Report: Generate static code metrics reports faster         Functionality Being Removed or Changed         Cache Efficiency: Store global block signal and state data operating at the same rate in one data structure                    | 7-28<br>7-30<br>7-30<br>7-30 |

| Verification                                                                                                                                                                                                                                                                                                          | 7-33                         |

| SIL and PIL Simulations: Advanced custom storage classes support<br>SIL and PIL Simulations: Support for imported grouped custom storage                                                                                                                                                                              | 7-33                         |

| classes                                                                                                                                                                                                                                                                                                               | 7-33<br>7-33                 |

| Check bug reports for issues and fixes                                                                                                                                                                                                                                                                                | 7-34                         |

| Code Generation from MATLAB Code                                                                                                                                                                                                                                                           | 8-2          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

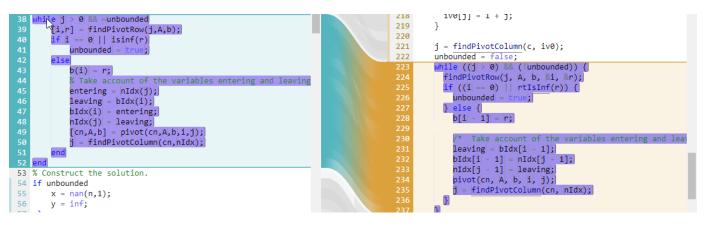

| Interactive Traceability: Visualize mapping between MATLAB code and C                                                                                                                                                                                                                      | 8-2          |

| codePolyspace Integration: Verify C/C++ code generated with MATLAB Coder by using simplified workflow                                                                                                                                                                                      | 8-2<br>8-2   |

| Changes to Setup for MISRA C Compliance: Disable dynamic memory allocation and set C standard math library to C99 (ISO)                                                                                                                                                                    | 8-2          |

| Model Architecture and Design                                                                                                                                                                                                                                                              | 8-4          |

| Embedded Coder Dictionary: Create custom code generation definitions for data and functions                                                                                                                                                                                                | 8-4          |

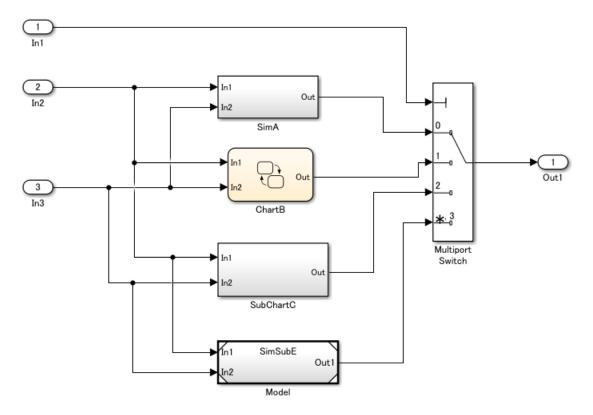

| Multi-Instance Code Generation: Apply more control when generating reusable, reentrant code                                                                                                                                                                                                | 8-4          |

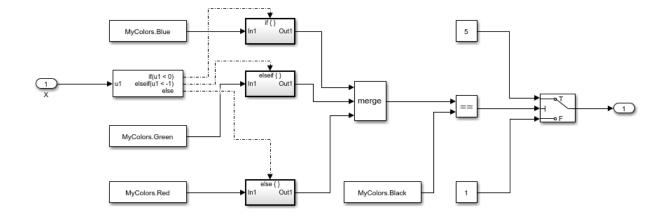

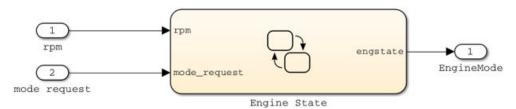

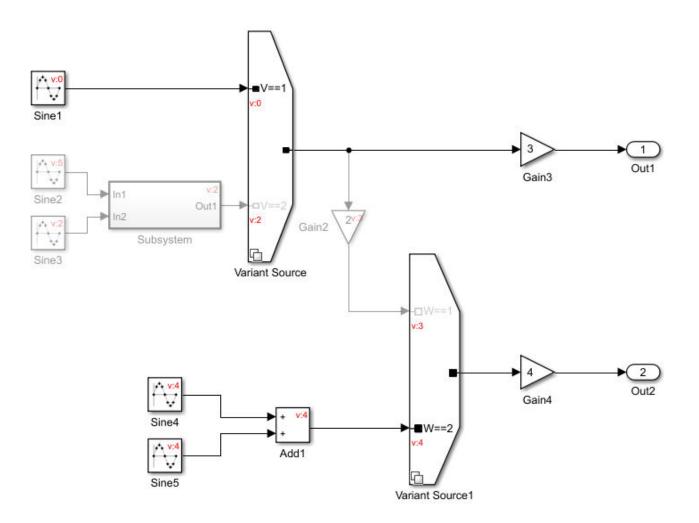

| Variant Blocks Usability Enhancement: Generate Preprocessor Conditionals<br>by using MATLAB variables as variant controls                                                                                                                                                                  | 8-5          |

| MISRA C:2012 Compliance and Deviation Considerations: Guidance for<br>evaluating your generated code for compliance with MISRA C:2012                                                                                                                                                      | o -          |

| directives and rules<br>Modeling Checks: Improve compliance of generated code by using Model<br>Advisor check for MISRA C:2012                                                                                                                                                             | 8-5<br>8-6   |

| AUTOSAR Release 4.3: Import and export AUTOSAR XML schema version 4.3                                                                                                                                                                                                                      | 8-6          |

| <ul> <li>AUTOSAR Perspective: Map and configure software components by using<br/>Code Mapping Editor and AUTOSAR Dictionary</li> <li>AUTOSAR XML Import and Export: Round-trip ComSpecs, import bitfield<br/>CompuMethods, export interface variation points, and automate more</li> </ul> | 8-6          |

| element creation                                                                                                                                                                                                                                                                           | 8-8<br>8-11  |

| NvMServiceCaller operations                                                                                                                                                                                                                                                                | 8-11<br>8-12 |

| Data, Function, and File Definition                                                                                                                                                                                                                                                        | 8-14         |

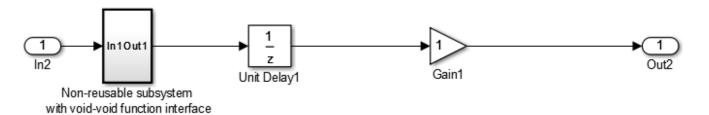

| Function-Prototype Control: Configure step function name with void void<br>interface                                                                                                                                                                                                       | 8-14         |

| across a model                                                                                                                                                                                                                                                                             | 8-14<br>8-15 |